I had two difficulties with the panelizer, but once I got beyond those, the process is quite easy. The troubles for me where:

- I’m a linux guy. The released version doesn’t run under mono. There’s a side version that works well

- I’m a kicad guy and the hackaday tutorial, while mentioning kicad, seems targeted at Eagle people. This is also easy to deal with if you know a couple key pieces of information.

Running on linux

When I run the released panelizer via the latest mono I could find for linux, I ran into the issue reported here, ie I get a message that contains this:System.ArgumentException: XOR data length expected Kicad related issues

The other issue I had was that the tutorial was written from the perspective of a non-kicad user. There are a couple things you have to watch for:- the panelizer is looking for a particular file extension for drilled holes

- the panelizer is looking for a particular file extension for the board outline

- and it is looking for particular file extensions for the layer files.

Drill file

Generate the drill file as normal. Just rename it to .txt. If you don’t do this, you’ll get a merged drl file and a merged txt file. the drl file will contain your original holes, properly translated to the panelized positions. The txt file will contain the holes needed for the break away tabs.Board outline

This a simple matter of renaming the gm1 file to gko.The layer files

You have to use the kicad plot option “Use Protel filename extensions”. Kicad gives a help message “this is no longer recommended”, which misled me for a bit. In this case, I recommend it.Simple panelizing directly in Kicad

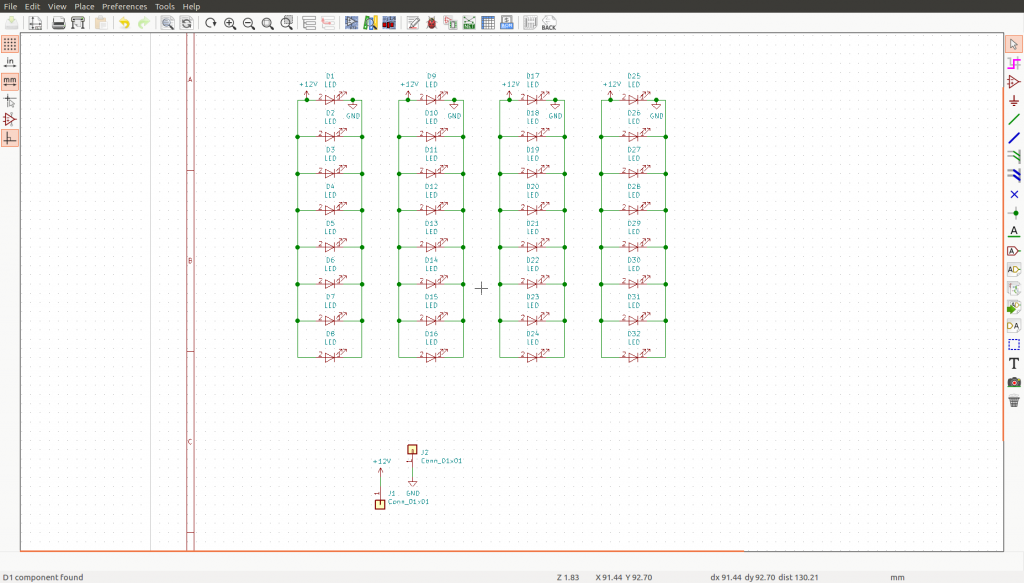

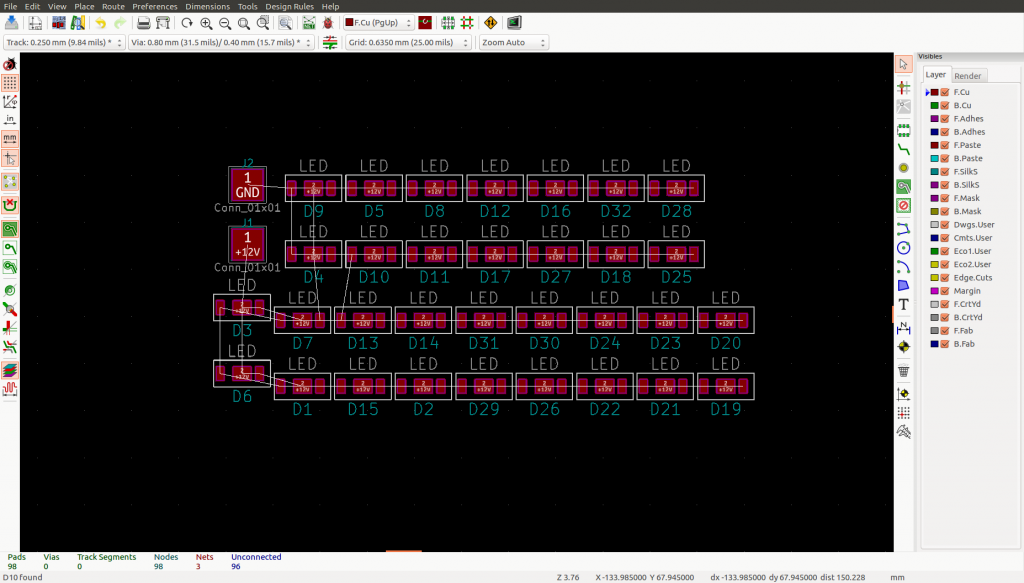

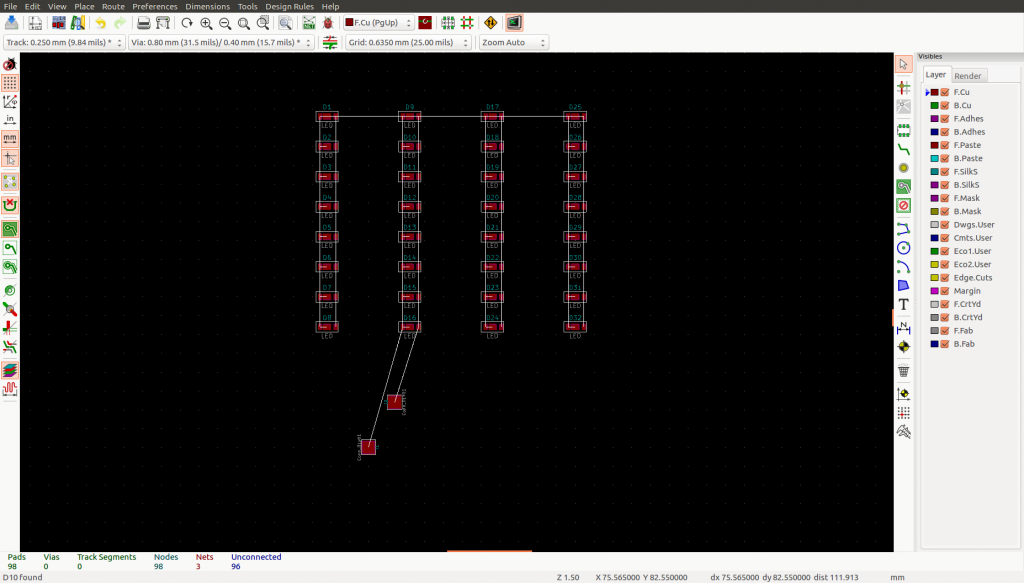

If you start pcbnew directly, 2 you’ll get the “append board” command in the file menu. So starting with a new board, append each design you want.Note that nets with the same net will get merged, so if you delete GND, all of ground will be deleted. You may also get opens reported.

You might find my gen_border script useful3, which will shrink a rectangular boarder around your design. It’ll also add a power and/or gnd zone on the same boundary.

A rant

The rest of this post adds nothing about how to panelize. Instead I want to rant a little.There are a bunch of services out there that offer cheap pcb fabrication for 10cmx10cm 2 layer boards. If you submit a set of gerbers that looks like multiple designs, they won’t make it for you. They want more money.

I recently did two small LED boards. They’re pretty small, so I put two of one and one of the other in a design and sent it off. denied.

Why?

My design has very few holes. The outline is not that complex, even with the added tabs. What’s the problem? I’m paying for 10×10 and 2 layers. I’m not ask for anything beyond that.

What’s the cheapest service that won’t hassle you for including multiple designs on one board? I am aware of pcbshopper.com. The problem is that even if you enter something other than 1 in the multiple designs field, the returned links won’t allow multiple designs. Also, dirtypcbs and seeed studio are said to be panelize friendly, but with shipping, you might as well buy multiple designs from a cheaper vendor. I think all this is a sign that I’m too cheap. I’m racing to the bottom.

Panelizing Kicad gerbers